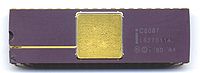

Intel 8087 - Intel 8087

Coprocessador matemático Intel 8087

| |

| Informação geral | |

|---|---|

| Lançado | 1980 |

| Comercializado por | Intel , IBM |

| Projetado por | Intel |

| Fabricante (s) comum (is) | |

| Desempenho | |

| Máx. Taxa de clock da CPU | 4 MHz a 10 MHz |

| Arquitetura e classificação | |

| Min. tamanho do recurso | 3 μm |

| Conjunto de instruções | x87 ( extensão do coprocessador de x86-16 ) |

| Especificações físicas | |

| Transistores | |

| Pacote (s) | |

| História | |

| Antecessor | 8231/8232 |

| Sucessor | 80287 |

O Intel 8087 , anunciado em 1980, foi o primeiro coprocessador de ponto flutuante x87 para a linha de microprocessadores 8086 .

O objetivo do 8087 era acelerar cálculos para aritmética de ponto flutuante, como adição , subtração , multiplicação , divisão e raiz quadrada . Ele também calculava funções transcendentais , como cálculos exponenciais , logarítmicos ou trigonométricos e, além de ponto flutuante, também podia operar em grandes números binários e decimais. As melhorias de desempenho foram de aproximadamente 20% a mais de 500%, dependendo da aplicação específica. O 8087 poderia executar cerca de 50.000 FLOPS usando cerca de 2,4 watts. Apenas as operações aritméticas se beneficiaram da instalação de um 8087; computadores usados apenas com aplicativos como processador de texto, por exemplo, não se beneficiariam com a despesa extra (cerca de US $ 150) e o consumo de energia de um 8087.

O 8087 foi um CI avançado para a época, ultrapassando os limites da tecnologia de fabricação da época. Os rendimentos iniciais foram extremamente baixos.

As vendas do 8087 receberam um aumento significativo quando a IBM incluiu um soquete de coprocessador na placa-mãe do IBM PC . Devido à escassez de chips, a IBM não ofereceu o 8087 como uma opção para o PC até que ele já estivesse no mercado há seis meses. O desenvolvimento do 8087 levou ao padrão IEEE 754-1985 para aritmética de ponto flutuante. Havia coprocessadores x87 posteriores para os processadores 80186 (não usados em compatíveis com PC), 80286, 80386 e 80386SX. A partir do 80486, os processadores Intel x86 posteriores não usavam um coprocessador de ponto flutuante separado; funções de ponto flutuante foram fornecidas integradas com o processador.

Internamente, o chip não tinha um multiplicador de hardware e cálculos implementados usando o algoritmo CORDIC .

Design e desenvolvimento

A Intel havia fabricado anteriormente a unidade de processamento aritmético 8231 e o processador de ponto flutuante 8232 . Eles foram projetados para uso com 8080 ou processadores semelhantes e usavam um barramento de dados de 8 bits. Eles tinham interface com um sistema host por meio de E / S programada ou um controlador DMA .

O 8087 foi inicialmente concebido por Bill Pohlman, o gerente de engenharia da Intel que supervisionou o desenvolvimento do chip 8086. Bill tomou medidas para ter certeza de que o chip 8086 poderia suportar um chip matemático ainda a ser desenvolvido.

Em 1977, Pohlman teve autorização para projetar o chip matemático 8087. Bruce Ravenel foi designado arquiteto e John Palmer foi contratado para ser o co-arquiteto e matemático do projeto. Os dois surgiram com um design revolucionário com 64 bits de mantissa e 16 bits de expoente para o número real de formato mais longo, com uma CPU de arquitetura de pilha e oito registradores de pilha de 80 bits, com um conjunto de instruções computacionalmente rico. O projeto resolveu alguns problemas conhecidos pendentes em computação numérica e software numérico: problemas de erro de arredondamento foram eliminados para operandos de 64 bits e conversões de modo numérico foram resolvidas para todos os números de 64 bits. Palmer creditou os escritos de William Kahan sobre ponto flutuante como uma influência significativa em seu design.

O design 8087 inicialmente teve uma recepção fria em Santa Clara devido ao seu design agressivo. Eventualmente, o design foi atribuído à Intel Israel, e Rafi Nave foi designado para liderar a implementação do chip. Palmer, Ravenel e Nave receberam patentes para o design. Robert Koehler e John Bayliss também receberam uma patente para a técnica em que algumas instruções com um padrão de bits específico foram transferidas para o coprocessador.

O 8087 tinha 45.000 transistores e foi fabricado como um circuito HMOS de carga de depleção de 3 μm . Funcionou em conjunto com o 8086 ou 8088 e introduziu cerca de 60 novas instruções . A maioria dos mnemônicos de montagem do 8087 começa com F, como FADD, FMUL, FCOM e assim por diante, tornando-os facilmente distinguíveis das instruções do 8086. As codificações binárias para todas as instruções 8087 começam com o padrão de bits 11011, decimal 27, o mesmo que o caractere ASCII ESC, embora nos bits de ordem superior de um byte; prefixos de instrução semelhantes às vezes também são chamados de " códigos de escape ". O mnemônico de instrução atribuído pela Intel para essas instruções do coprocessador é "ESC".

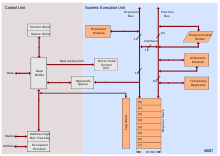

Quando a CPU 8086 ou 8088 executou a instrução ESC, se o segundo byte (o byte ModR / M) especificou um operando de memória, a CPU executaria um ciclo de barramento para ler uma palavra do local de memória especificado na instrução (usando qualquer 8086 modo de endereçamento), mas não armazenaria o operando lido em nenhum registro da CPU ou realizaria qualquer operação nele; o 8087 observaria o barramento e decodificaria o fluxo de instruções em sincronia com o 8086, reconhecendo as instruções do coprocessador destinadas a si mesmo. Para uma instrução 8087 com um operando de memória, se a instrução solicitasse a leitura do operando, o 8087 retiraria a palavra de dados lida pela CPU principal do barramento de dados. Se o operando a ser lido tivesse mais de uma palavra, o 8087 também copiaria o endereço do barramento de endereços; então, após a conclusão do ciclo de leitura de dados conduzido pela CPU, o 8087 usaria imediatamente o DMA para assumir o controle do barramento e transferir os bytes adicionais do próprio operando. Se uma instrução 8087 com um operando de memória solicitasse a escrita desse operando, o 8087 ignoraria a palavra lida no barramento de dados e apenas copiaria o endereço, então solicitaria o DMA e escreveria todo o operando, da mesma forma que faria o fim de um operando estendido. Desta forma, a CPU principal mantinha o controle geral do barramento e da sincronização do barramento, enquanto o 8087 tratava de todos os outros aspectos da execução das instruções do coprocessador, exceto por breves períodos de DMA, quando o 8087 assumia o controle do barramento para ler ou gravar operandos para / de seus próprios registros internos. Como conseqüência deste projeto, o 8087 só poderia operar em operandos retirados da memória ou de seus próprios registradores, e qualquer troca de dados entre o 8087 e o 8086 ou 8088 era somente por meio de RAM.

O programa principal da CPU continuou a ser executado enquanto o 8087 executava uma instrução; da perspectiva da CPU principal do 8086 ou 8088, uma instrução do coprocessador demorava apenas o tempo do processamento do opcode e de qualquer ciclo do operando da memória (2 ciclos de clock para nenhum operando, 8 ciclos de clock mais o tempo de cálculo do EA [5 a 12 clock ciclos] para um operando de memória [mais 4 ciclos de clock em um 8088], para transferir o segundo byte da palavra do operando), após o qual a CPU começaria a executar a próxima instrução do programa. Assim, um sistema com um 8087 era capaz de processamento paralelo verdadeiro, realizando uma operação na ALU inteira da CPU principal enquanto ao mesmo tempo realizava uma operação de ponto flutuante no coprocessador 8087. Como o 8086 ou 8088 controlava exclusivamente o fluxo e o tempo das instruções e não tinha acesso direto ao status interno do 8087, e como o 8087 podia executar apenas uma instrução por vez, programas para o sistema combinado 8086/8087 ou 8088/8087 teve que garantir que o 8087 tivesse tempo para completar a última instrução emitida a ele antes de ser emitida outra. A instrução WAIT (da CPU principal) foi fornecida para esse propósito, e a maioria dos montadores afirmava implicitamente uma instrução WAIT antes de cada instância da maioria das instruções do coprocessador de ponto flutuante. (Não é necessário usar uma instrução WAIT antes de uma operação 8087 se o programa usar outros meios para garantir que tempo suficiente passe entre a emissão das instruções 8087 sensíveis ao tempo para que o 8087 nunca possa receber tal instrução antes de completar o anterior um. Também não é necessário, se um WAIT for usado, que preceda imediatamente a próxima instrução 8087.) A instrução WAIT esperou que o pino de entrada −TEST do 8086/8088 fosse declarado (baixo), e este pino foi conectado ao pino BUSY do 8087 em todos os sistemas que tinham um 8087 (então TEST foi confirmado quando BUSY foi desabilitado).

Como as filas de pré-busca de instruções do 8086 e 8088 fazem com que o momento em que uma instrução seja executada nem sempre seja o mesmo que o momento em que é buscada, um coprocessador como o 8087 não pode determinar quando uma instrução para si é a próxima instrução a ser executada puramente observando o barramento da CPU. O 8086 e o 8088 têm dois sinais de status de fila conectados ao coprocessador para permitir que ele sincronize com o tempo interno da CPU de execução de instruções de sua fila de pré-busca. O 8087 mantém sua própria fila de pré-busca idêntica, a partir da qual lê os opcodes do coprocessador que realmente executa. Como as filas de pré-busca do 8086 e 8088 têm tamanhos diferentes e algoritmos de gerenciamento diferentes, o 8087 determina a qual tipo de CPU está conectado, observando uma determinada linha de barramento da CPU quando o sistema é reiniciado, e o 8087 ajusta sua fila de instruções interna de acordo. A duplicação redundante do hardware da fila de pré-busca na CPU e no coprocessador é ineficiente em termos de uso de energia e área total de dados, mas permitiu que a interface do coprocessador usasse muito poucos pinos IC dedicados, o que era importante. Na época em que o 8086, que definiu a interface do coprocessador, foi introduzido, os pacotes de IC com mais de 40 pinos eram raros, caros e repletos de problemas como capacitância excessiva do cabo, um fator limitante importante para as velocidades de sinalização.

Os códigos de operação do coprocessador são codificados em 6 bits em 2 bytes, começando com a sequência de escape:

┌───────────┬───────────┐ │ 1101 1xxx │ mmxx xrrr │ └───────────┴───────────┘

Os primeiros três bits "x" são os três primeiros bits do opcode de ponto flutuante. Em seguida, dois bits "m", depois a última metade dos três bits do opcode de ponto flutuante, seguidos por três bits "r". Os bits "m" e "r" especificam as informações do modo de endereçamento.

Os programas aplicativos tiveram que ser escritos para fazer uso das instruções especiais de ponto flutuante. Em tempo de execução, o software pode detectar o coprocessador e usá-lo para operações de ponto flutuante. Quando detectado ausente, funções de ponto flutuante semelhantes tiveram que ser calculadas no software, ou todo o coprocessador poderia ser emulado no software para compatibilidade numérica mais precisa.

Registros

A família x87 não usa um conjunto de registros endereçáveis diretamente , como os registros principais dos processadores x86; em vez disso, os registradores x87 formam uma estrutura deep stack de oito níveis variando de st0 a st7, onde st0 é o topo. As instruções x87 operam empurrando, calculando e colocando valores nesta pilha. No entanto, as operações diádicas como FADD, FMUL, FCMP e assim por diante podem usar implicitamente o st0 e st1 mais acima ou podem usar st0 junto com um operando ou registrador de memória explícita ; o registrador st0 pode então ser usado como um acumulador (isto é, como um destino combinado e operando esquerdo) e também pode ser trocado com qualquer um dos oito registradores da pilha usando uma instrução chamada FXCH st X (códigos D9C8-D9CF h ). Isso torna a pilha x87 utilizável como sete registradores endereçáveis livremente mais um acumulador. Isso é especialmente aplicável em processadores superescalares x86 ( Pentium de 1993 e posterior), onde essas instruções de troca são otimizadas para uma penalidade de clock zero.

Padrão de ponto flutuante IEEE

Quando a Intel projetou o 8087, seu objetivo era fazer um formato de ponto flutuante padrão para projetos futuros. Um aspecto importante do 8087 de uma perspectiva histórica foi que ele se tornou a base para o padrão de ponto flutuante IEEE 754 . O 8087 não implementou o eventual padrão IEEE 754 em todos os seus detalhes, já que o padrão não foi concluído até 1985, mas o 80387 sim. A 8087 fornecida dois básicas 32 / 64-bit tipos de dados de ponto flutuante e um adicional de 80-bit estendida formato interno temporário (que também pode ser armazenada na memória) para melhorar a precisão sobre cálculos grandes e complexas. Além disso, o 8087 oferecia um formato BCD compactado de 80 bits / 18 dígitos ( decimal codificado em binário ) e tipos de dados inteiros de 16, 32 e 64 bits.

| 8087 tipos de dados | |||||||||||||||||

| 7 9 | ... | 7 1 | ... | 6 7 | ... | 6 3 | ... | 5 0 | ... | 3 1 | ... | 2 2 | ... | 1 5 | ... | 0 0 | (posição do bit) |

| ± | Expoente | Fração | Precisão estendida de 80 bits real | ||||||||||||||

| ± | Expoente | Fração | Real de dupla precisão de 64 bits | ||||||||||||||

| ± | Expoente | Fração | Real de precisão simples de 32 bits | ||||||||||||||

| ± | BCD Inteiro | Inteiro decimal de 18 dígitos | |||||||||||||||

| ± | Inteiro | Inteiro binário de 64 bits | |||||||||||||||

| ± | Inteiro | Inteiro binário de 32 bits | |||||||||||||||

| ± | Inteiro | Inteiro binário de 16 bits | |||||||||||||||

Infinidade

O 8087 lida com valores infinitos por fechamento afim ou fechamento projetivo (selecionado pelo registro de status). Com o fechamento afim, infinitos positivos e negativos são tratados como valores diferentes. Com o fechamento projetivo, o infinito é tratado como uma representação sem sinal para números muito pequenos ou muito grandes. Esses dois métodos de tratamento do infinito foram incorporados à versão preliminar do padrão de ponto flutuante IEEE 754 . No entanto, o fechamento projetivo ( sistema de número real estendido projetivamente ) foi retirado da edição formal posterior do IEEE 754-1985. O 80287 manteve o fechamento projetivo como uma opção, mas o 80387 e os processadores de ponto flutuante subsequentes (incluindo o 80187) suportaram apenas o fechamento afim.

Interface do coprocessador

O 8087 era diferente dos coprocessadores Intel subseqüentes por estar diretamente conectado aos barramentos de endereço e dados. O 8087 procurava instruções que começavam com a sequência "11011" e agia sobre elas, imediatamente solicitando DMA da CPU principal conforme necessário para acessar operandos de memória com mais de uma palavra (16 bits), então liberando imediatamente o controle de barramento de volta para a CPU principal . O coprocessador não atrasou a execução do programa até que a instrução do coprocessador fosse concluída e o programa teve que sincronizar explicitamente os dois processadores, conforme explicado acima (na seção " Design e desenvolvimento "). Havia um possível problema de travamento se a instrução do coprocessador falhou ao decodificar para uma que o coprocessador entendeu. Os coprocessadores posteriores da Intel não se conectavam aos barramentos da mesma maneira, mas recebiam instruções por meio das portas de E / S do processador principal. Isso gerava uma penalidade no tempo de execução, mas o problema potencial de travamento foi evitado porque o processador principal ignoraria a instrução se o coprocessador se recusasse a aceitá-la. O 8087 foi capaz de detectar se estava conectado a um 8088 ou 8086 monitorando o barramento de dados durante o ciclo de reinicialização.

O 8087 era, em teoria, capaz de funcionar simultaneamente enquanto o 8086/8 processava instruções adicionais. Na prática, havia o potencial de falha do programa se o coprocessador emitisse uma nova instrução antes que a última fosse concluída. O montador inseriria automaticamente uma instrução FWAIT após cada opcode do coprocessador, forçando o 8086/8 a interromper a execução até que o 8087 sinalizasse que havia terminado. Esta limitação foi removida de designs posteriores.

Modelos e fontes secundárias

Os coprocessadores Intel 8087 foram fabricados em duas variantes: uma com DIP soldada lateralmente em cerâmica (CerDIP) e outra em DIP hermético (PDIP), e foram projetados para operar nas seguintes faixas de temperatura:

- Prefixos C, D, QC e QD: 0 ° C a +70 ° C (uso comercial).

- Prefixos LC, LD, TC e TD: −40 ° C a +85 ° C (uso industrial).

- Prefixos MC e MD: −55 ° C a +125 ° C (uso militar).

Todos os modelos do 8087 tinham um encapsulamento DIP de 40 pinos e operavam com 5 volts, consumindo cerca de 2,4 watts. Ao contrário dos coprocessadores Intel posteriores, o 8087 precisava rodar na mesma velocidade de clock do processador principal. Sufixos no número da peça identificam a velocidade do clock:

| Número do modelo | Frequência |

|---|---|

| Intel 8087 | 5 MHz |

| Intel 8087-1 | 10 MHz |

| Intel 8087-2 | 8 MHz |

| Intel 8087-3 | 4 MHz |

| Intel 8087-6 | 6 MHz |

A parte foi segunda-sourced pela AMD como AMD 8087 e por Cyrix como Cyrix 8087. O clone K1810WM87 do 8087 foi produzido na União Soviética .

Sucessores

Assim como os processadores 8088 e 8086 foram substituídos por partes posteriores, o 8087 também foi substituído. Outros coprocessadores Intel foram o 80287 , 80387 e o 80187 . A partir do 80486, os processadores Intel posteriores não usavam um coprocessador de ponto flutuante separado; praticamente tudo incluído no chip do processador principal, com exceção significativa do 80486SX, que foi um 80486DX modificado com a FPU desabilitada. O 80487 era na verdade um chip 80486DX completo com um pino extra. Quando instalado, ele desabilitou a CPU 80486SX. Os processadores 80486DX , Pentium e posteriores incluem funcionalidade de ponto flutuante no núcleo da CPU.

Referências

Bibliografia

- Sanchez, Julio; Canton, Maria P. (2007). Soluções de software para engenheiros e cientistas . CRC Press. ISBN 1-4200-4302-1.

links externos

- Coprocessadores matemáticos Intel 80x87 em cpu-collection.de

- Coprocessor.info: informações e imagens do histórico do coprocessador matemático 8087

- Folha de dados para o coprocessador matemático Intel 8087

- Shirriff, Ken (maio de 2020). "Análise de dados do rápido bit shifter do coprocessador matemático 8087" .