Hierarquia de cache - Cache hierarchy

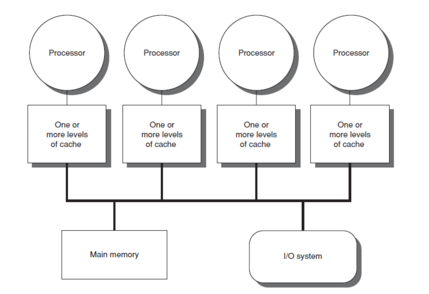

Hierarquia de cache, ou caches de vários níveis , refere-se a uma arquitetura de memória que usa uma hierarquia de armazenamentos de memória com base em velocidades de acesso variáveis aos dados de cache. Os dados altamente solicitados são armazenados em cache em armazenamentos de memória de acesso de alta velocidade, permitindo um acesso mais rápido pelos núcleos da unidade central de processamento (CPU).

A hierarquia de cache é uma forma e parte da hierarquia de memória e pode ser considerada uma forma de armazenamento em camadas . Esse design foi projetado para permitir que os núcleos da CPU processem mais rápido, apesar da latência de memória do acesso à memória principal . Acessar a memória principal pode atuar como um gargalo para o desempenho do núcleo da CPU enquanto a CPU espera pelos dados, enquanto tornar toda a memória principal em alta velocidade pode ser proibitivamente caro. Caches de alta velocidade são um compromisso que permite acesso em alta velocidade aos dados mais usados pela CPU, permitindo um clock da CPU mais rápido .

Fundo

Na história do desenvolvimento de computadores e chips eletrônicos, houve um período em que os aumentos na velocidade da CPU ultrapassaram as melhorias na velocidade de acesso à memória. A diferença entre a velocidade das CPUs e a memória significava que a CPU muitas vezes ficava ociosa. As CPUs eram cada vez mais capazes de rodar e executar grandes quantidades de instruções em um determinado tempo, mas o tempo necessário para acessar os dados da memória principal impedia que os programas se beneficiassem totalmente desse recurso. Este problema motivou a criação de modelos de memória com taxas de acesso mais altas para perceber o potencial de processadores mais rápidos.

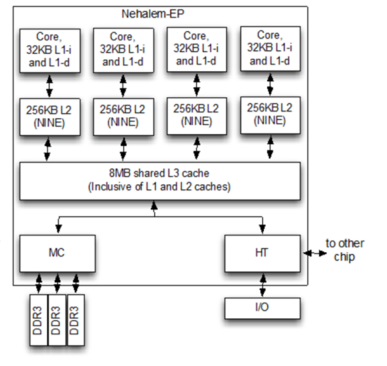

Isso resultou no conceito de memória cache , proposto pela primeira vez por Maurice Wilkes , um cientista da computação britânico na Universidade de Cambridge em 1965. Ele chamou esses modelos de memória de "memória escrava". Entre aproximadamente 1970 e 1990, documentos e artigos de Anant Agarwal , Alan Jay Smith , Mark D. Hill , Thomas R. Puzak e outros discutiram melhores designs de memória cache. Os primeiros modelos de memória cache foram implementados na época, mas mesmo enquanto os pesquisadores investigavam e propunham projetos melhores, a necessidade de modelos de memória mais rápidos continuava. Essa necessidade resultou do fato de que, embora os primeiros modelos de cache melhorassem a latência de acesso aos dados, em relação ao custo e às limitações técnicas, não era viável para o cache de um sistema de computador se aproximar do tamanho da memória principal. A partir de 1990, ideias como adicionar outro nível de cache (segundo nível), como backup para o cache de primeiro nível, foram propostas. Jean-Loup Baer , Wen-Hann Wang, Andrew W. Wilson e outros conduziram pesquisas sobre esse modelo. Quando várias simulações e implementações demonstraram as vantagens dos modelos de cache de dois níveis, o conceito de caches de vários níveis se popularizou como um modelo novo e geralmente melhor de memórias cache. Desde 2000, os modelos de cache multinível têm recebido grande atenção e atualmente são implementados em muitos sistemas, como os caches de três níveis que estão presentes nos produtos Core i7 da Intel.

Cache multinível

Acessar a memória principal para cada execução de instrução pode resultar em processamento lento, com a velocidade do clock dependendo do tempo necessário para localizar e buscar os dados. Para ocultar essa latência de memória do processador, o armazenamento em cache de dados é usado. Sempre que os dados são exigidos pelo processador, eles são buscados na memória principal e armazenados em uma estrutura de memória menor, chamada de cache. Se houver alguma necessidade adicional desses dados, o cache é pesquisado primeiro, antes de ir para a memória principal. Essa estrutura reside mais perto do processador em termos de tempo gasto para pesquisar e buscar dados em relação à memória principal. As vantagens de usar o cache podem ser comprovadas calculando o tempo médio de acesso (AAT) para a hierarquia de memória com e sem o cache.

Tempo médio de acesso (AAT)

Os caches, sendo de tamanho pequeno, podem resultar em erros frequentes - quando uma pesquisa no cache não fornece as informações desejadas - resultando em uma chamada à memória principal para buscar dados. Conseqüentemente, o AAT é afetado pela taxa de erros de cada estrutura a partir da qual ele busca os dados.

O AAT para a memória principal é dado pela memória principal de tempo de hit . AAT para caches pode ser fornecido por

- Cache de tempo de acerto + ( cache de taxa de falha × tempo de penalidade de falha para ir para a memória principal após a perda de cache ).

O tempo de acerto para caches é menor que o tempo de acerto para a memória principal, portanto, o AAT para recuperação de dados é significativamente menor ao acessar dados por meio do cache em vez da memória principal.

Trade-offs

Embora o uso do cache possa melhorar a latência da memória, nem sempre pode resultar na melhoria necessária para o tempo gasto para buscar dados devido à maneira como os caches são organizados e percorridos. Por exemplo, caches mapeados diretamente que são do mesmo tamanho geralmente têm uma taxa de falha mais alta do que caches totalmente associativos. Isso também pode depender do benchmark do computador testando o processador e do padrão de instruções. Mas usar um cache totalmente associativo pode resultar em mais consumo de energia, já que é necessário pesquisar todo o cache todas as vezes. Devido a isso, a compensação entre o consumo de energia (e o calor associado) e o tamanho do cache torna-se crítica no design do cache.

Evolução

No caso de uma falha de cache, o propósito de usar tal estrutura se tornará inútil e o computador terá que ir para a memória principal para buscar os dados necessários. No entanto, com um cache de vários níveis , se o computador perder o cache mais próximo do processador (cache de nível um ou L1), ele pesquisará os próximos níveis mais próximos de cache e irá para a memória principal apenas se estes métodos falham. A tendência geral é manter o cache L1 pequeno e a uma distância de 1–2 ciclos de clock da CPU do processador, com os níveis mais baixos de caches aumentando em tamanho para armazenar mais dados do que L1, sendo, portanto, mais distante, mas com menos perda avaliar. Isso resulta em um AAT melhor. O número de níveis de cache pode ser projetado por arquitetos de acordo com seus requisitos após verificar as compensações entre custo, AATs e tamanho.

Ganhos de desempenho

Com o escalonamento da tecnologia que permitiu que os sistemas de memória pudessem ser acomodados em um único chip, a maioria dos processadores modernos tem até três ou quatro níveis de cache. A redução no AAT pode ser entendida por este exemplo, onde o computador verifica o AAT para diferentes configurações de até caches L3.

Exemplo : memória principal = 50 ns , L1 = 1 ns com taxa de falha de 10%, L2 = 5 ns com taxa de falha de 1%), L3 = 10 ns com taxa de falha de 0,2%.

- Sem cache, AAT = 50 ns

- Cache L1, AAT = 1 ns + (0,1 × 50 ns) = 6 ns

- Caches L1–2, AAT = 1 ns + (0,1 × [5 ns + (0,01 × 50 ns)]) = 1,55 ns

- Caches L1–3, AAT = 1 ns + (0,1 × [5 ns + (0,01 × [10 ns + (0,002 × 50 ns)])]) = 1,5101 ns

Desvantagens

- A memória cache tem um custo marginal maior do que a memória principal e, portanto, pode aumentar o custo do sistema geral.

- Os dados em cache são armazenados apenas enquanto a energia for fornecida ao cache.

- Aumento da área no chip necessária para o sistema de memória.

- Os benefícios podem ser minimizados ou eliminados no caso de programas grandes com localidade temporal pobre , que freqüentemente acessam a memória principal.

Propriedades

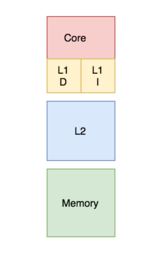

Bancado versus unificado

Em um cache armazenado, o cache é dividido em um cache dedicado ao armazenamento de instruções e um cache dedicado aos dados. Em contraste, um cache unificado contém as instruções e os dados no mesmo cache. Durante um processo, o cache L1 (ou a maior parte do cache de nível superior em relação à sua conexão com o processador) é acessado pelo processador para recuperar instruções e dados. Exigir que as duas ações sejam implementadas ao mesmo tempo requer várias portas e mais tempo de acesso em um cache unificado. Ter várias portas requer hardware e fiação adicionais, levando a uma estrutura significativa entre os caches e as unidades de processamento. Para evitar isso, o cache L1 geralmente é organizado como um cache armazenado, o que resulta em menos portas, menos hardware e, geralmente, tempos de acesso mais baixos.

Os processadores modernos têm caches divididos e, em sistemas com caches de vários níveis, os caches de nível superior podem ser unificados enquanto os níveis inferiores são divididos.

Políticas de Inclusão

Se um bloco presente na camada de cache superior também pode estar presente no nível de cache inferior é governado pela política de inclusão do sistema de memória, que pode ser inclusiva, exclusiva ou não inclusiva não exclusiva (NOVE).

Com uma política inclusiva, todos os blocos presentes no cache de nível superior também devem estar presentes no cache de nível inferior. Cada componente de cache de nível superior é um subconjunto do componente de cache de nível inferior. Neste caso, como há duplicação de blocos, ocorre algum desperdício de memória. No entanto, a verificação é mais rápida.

Sob uma política exclusiva, todos os componentes da hierarquia do cache são completamente exclusivos, de forma que qualquer elemento no cache de nível superior não estará presente em nenhum dos componentes do cache inferior. Isso permite o uso completo da memória cache. No entanto, há uma alta latência de acesso à memória.

As políticas acima requerem um conjunto de regras a serem seguidas para implementá-las. Se nenhum deles for forçado, a política de inclusão resultante é chamada de não inclusiva não exclusiva (NOVE). Isso significa que o cache de nível superior pode ou não estar presente no cache de nível inferior.

Escreva políticas

Existem duas políticas que definem a forma como um bloco de cache modificado será atualizado na memória principal: write through e write back.

No caso de gravação por meio da política, sempre que o valor do bloco de cache muda, ele também é modificado na hierarquia de memória de nível inferior. Essa política garante que os dados sejam armazenados com segurança à medida que são gravados em toda a hierarquia.

No entanto, no caso da política de write-back, o bloco de cache alterado será atualizado na hierarquia de nível inferior apenas quando o bloco de cache for removido. Um "bit sujo" é anexado a cada bloco de cache e definido sempre que o bloco de cache é modificado. Durante o despejo, os blocos com um bit incorreto definido serão gravados na hierarquia de nível inferior. De acordo com esta política, existe o risco de perda de dados, pois a cópia alterada mais recentemente de um dado é armazenada apenas no cache e, portanto, algumas técnicas corretivas devem ser observadas.

No caso de uma gravação onde o byte não está presente no bloco de cache, o byte pode ser trazido para o cache conforme determinado por uma política de alocação de gravação ou não alocação de gravação. A política de alocação de gravação afirma que, em caso de falha de gravação, o bloco é obtido da memória principal e colocado no cache antes da gravação. Na política de gravação de não alocação, se o bloco for perdido no cache, ele gravará na hierarquia de memória de nível inferior sem buscar o bloco no cache.

As combinações comuns das políticas são "bloco de gravação", "alocação de gravação" e "gravação por meio de gravação sem alocação" .

Um cache privado é atribuído a um determinado núcleo em um processador e não pode ser acessado por nenhum outro núcleo. Em algumas arquiteturas, cada núcleo tem seu próprio cache privado; isso cria o risco de blocos duplicados na arquitetura de cache do sistema, o que resulta na redução da utilização da capacidade. No entanto, esse tipo de escolha de design em uma arquitetura de cache de várias camadas também pode ser bom para uma latência de acesso a dados mais baixa.

Um cache compartilhado é um cache que pode ser acessado por vários núcleos. Por ser compartilhado, cada bloco no cache é único e, portanto, tem uma taxa de acerto maior, pois não haverá blocos duplicados. No entanto, a latência de acesso aos dados pode aumentar à medida que vários núcleos tentam acessar o mesmo cache.

Em processadores com vários núcleos , a escolha do projeto de fazer um cache compartilhado ou privado afeta o desempenho do processador. Na prática, o cache de nível superior L1 (ou às vezes L2) é implementado como privado e os caches de nível inferior são implementados como compartilhado. Este projeto fornece altas taxas de acesso para os caches de alto nível e baixas taxas de falha para os caches de nível inferior.

Modelos de implementação recentes

Microarquitetura Intel Broadwell (2014)

- Cache L1 (instrução e dados) - 64 kB por núcleo

- Cache L2 - 256 kB por núcleo

- Cache L3 - 2 MB a 6 MB compartilhados

- Cache L4 - 128 MB de eDRAM (apenas modelos Iris Pro)

Microarquitetura Intel Kaby Lake (2016)

- Cache L1 (instrução e dados) - 64 kB por núcleo

- Cache L2 - 256 kB por núcleo

- Cache L3 - 2 MB a 8 MB compartilhados

Microarquitetura Zen da AMD (2017)

- Cache L1 - dados de 32 kB e instrução de 64 kB por núcleo, 4 vias

- Cache L2 - 512 kB por núcleo, 4 vias inclusive

- Cache L3 - 4 MB local e remoto por CCX de 4 núcleos, 2 CCXs por chip, 16 vias não incluídas. Até 16 MB em CPUs de desktop e 64 MB em CPUs de servidor

Microarquitetura AMD Zen 2 (2019)

- Cache L1 - dados de 32 kB e instrução de 32 kB por núcleo, 8 vias

- Cache L2 - 512 kB por núcleo, 8 vias inclusive

- Cache L3 - 16 MB local por CCX de 4 núcleos, 2 CCXs por chip, 16 vias não incluídas. Até 64 MB em CPUs de desktop e 256 MB em CPUs de servidor

IBM Power 7

- Cache L1 (instrução e dados) - cada banco de 64, cada banco tem 2ª + 1 porta de gravação de 32 kB, associativa de 8 vias, bloco de 128B, gravação

- Cache L2 - 256 kB, 8 vias, bloco de 128B, write-back, incluindo L1, latência de acesso de 2 ns

- Cache L3 - 8 regiões de 4 MB (total de 32 MB), região local 6 ns, remoto 30 ns, cada região associativa de 8 vias, matriz de dados DRAM, matriz de tag SRAM

Veja também

- Power7

- Microarquitetura Intel Broadwell

- Microarquitetura Intel Kaby Lake

- CPU Cache

- Hierarquia de memória

- Latência CAS

- Cache (computação)